Pag-optimize ng quantum circuit

Toshinari Itoko (21 Hunyo 2024)

I-download ang pdf ng orihinal na lektura. Tandaan na maaaring ma-deprecated na ang ilang code snippets dahil static na mga larawan ang mga ito.

Tinatayang QPU time para patakbuhin ang eksperimentong ito ay 15 s.

(Tala: Ilang cell ng bahagi 2 ay kinopya mula sa notebook na "Qiskit Deep dive", isinulat ni Matthew Treinish (Qiskit maintainer))

# Added by doQumentation — required packages for this notebook

!pip install -q qiskit qiskit-aer qiskit-ibm-runtime

# !pip install 'qiskit[visualization]'

# !pip install qiskit_ibm_runtime qiskit_aer

# !pip install jupyter

# !pip install matplotlib pylatexenc pydot pillow

import qiskit

qiskit.__version__

'2.0.2'

import qiskit_ibm_runtime

qiskit_ibm_runtime.__version__

'0.40.1'

import qiskit_aer

qiskit_aer.__version__

'0.17.1'

1. Panimula

Tatalakayin ng araling ito ang ilang aspeto ng pag-optimize ng circuit sa quantum computing. Sa partikular, makikita natin ang halaga ng pag-optimize ng circuit sa pamamagitan ng paggamit ng mga built-in na optimization setting ng Qiskit. Pagkatapos ay susuriin natin nang mas malalim kung ano ang magagawa mo bilang isang eksperto sa iyong partikular na larangan ng aplikasyon para bumuo ng mga circuit sa matalinong paraan. Sa wakas, maingat nating susuriin kung ano ang nangyayari sa panahon ng transpilation na tumutulong sa atin na i-optimize ang ating mga circuit.

2. Mahalaga ang pag-optimize ng circuit

Una, ikukumpara natin ang mga resulta ng pagpapatakbo ng mga circuit para sa paghahanda ng 5-qubit na GHZ state () — isa na may optimization at isa na wala.

from qiskit.circuit import QuantumCircuit

from qiskit.transpiler.preset_passmanagers import generate_preset_pass_manager

from qiskit.primitives import BackendSamplerV2 as Sampler

from qiskit_ibm_runtime.fake_provider import FakeBrisbane

backend = FakeBrisbane()

Una, gagamitin natin ang isang GHZ circuit na simpleng na-synthesize tulad ng sumusunod.

num_qubits = 5

ghz_circ = QuantumCircuit(num_qubits)

ghz_circ.h(0)

[ghz_circ.cx(0, i) for i in range(1, num_qubits)]

ghz_circ.measure_all()

ghz_circ.draw("mpl")

2.1 Antas ng optimization

Mayroong 4 na available na optimization_level mula 0 hanggang 3. Habang tumataas ang antas ng optimization, mas maraming computational effort ang ginagastos para i-optimize ang circuit. Ang Level 0 ay walang optimization at gumagawa lamang ng pinakamaliit na trabaho para mapatakbo ang circuit sa napiling backend. Ang Level 3 ay gumagastos ng pinakamataas na pagsisikap (at karaniwang runtime) para subukang i-optimize ang circuit. Ang Level 1 ang default na antas ng optimization.

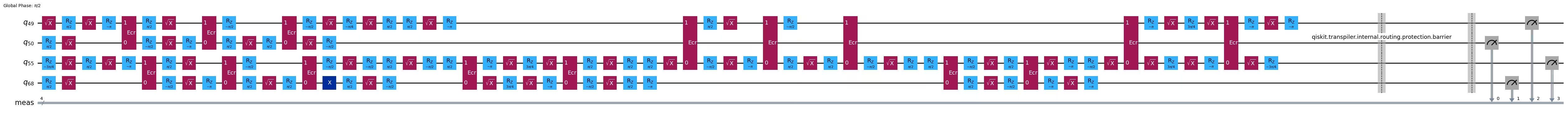

Tina-transpile natin ang circuit nang walang optimization (optimization_level=0) at na may optimization (optimization_level=2).

Makikita natin ang malaking pagkakaiba sa haba ng mga na-transpile na circuit.

pm0 = generate_preset_pass_manager(

optimization_level=0, backend=backend, seed_transpiler=777

)

pm2 = generate_preset_pass_manager(

optimization_level=2, backend=backend, seed_transpiler=777

)

circ0 = pm0.run(ghz_circ)

circ2 = pm2.run(ghz_circ)

print("optimization_level=0:")

display(circ0.draw("mpl", idle_wires=False, fold=-1))

print("optimization_level=2:")

display(circ2.draw("mpl", idle_wires=False, fold=-1))

optimization_level=0:

optimization_level=2:

2.2 Ehersisyo

Subukan din ang optimization_level=1 at ikumpara ang resultang circuit sa dalawa sa itaas. Subukan ito sa pamamagitan ng pagbabago ng code sa itaas.

Solusyon:

pm1 = generate_preset_pass_manager(

optimization_level=1, backend=backend, seed_transpiler=777

)

circ1 = pm1.run(ghz_circ)

print("optimization_level=1:")

display(circ1.draw("mpl", idle_wires=False, fold=-1))

optimization_level=1:

Patakbuhin sa isang fake backend (maingay na simulation). Tingnan ang Appendix 1 para sa kung paano patakbuhin sa isang tunay na backend.

# run the circuits on the fake backend (noisy simulator)

sampler = Sampler(backend=backend)

job = sampler.run([circ0, circ2], shots=10000)

print(f"Job ID: {job.job_id()}")

Job ID: 93a4ac70-e3ea-44ad-aea9-5045840c9076

# get results

result = job.result()

unoptimized_result = result[0].data.meas.get_counts()

optimized_result = result[1].data.meas.get_counts()

from qiskit.visualization import plot_histogram

# plot

sim_result = {"0" * 5: 0.5, "1" * 5: 0.5}

plot_histogram(

[result for result in [sim_result, unoptimized_result, optimized_result]],

bar_labels=False,

legend=[

"ideal",

"no optimization",

"with optimization",

],

)

3. Mahalaga rin ang circuit synthesis

Susunod, ikukumpara natin ang mga resulta ng pagpapatakbo ng dalawang naiibang na-synthesize na circuit para sa paghahanda ng 5-qubit na GHZ state ().

# Original GHZ circuit (naive synthesis)

ghz_circ.draw("mpl")

# A cleverly-synthesized GHZ circuit

ghz_circ2 = QuantumCircuit(5)

ghz_circ2.h(2)

ghz_circ2.cx(2, 1)

ghz_circ2.cx(2, 3)

ghz_circ2.cx(1, 0)

ghz_circ2.cx(3, 4)

ghz_circ2.measure_all()

ghz_circ2.draw("mpl")

# transpile both with the same optimization level 2

circ_org = pm2.run(ghz_circ)

circ_new = pm2.run(ghz_circ2)

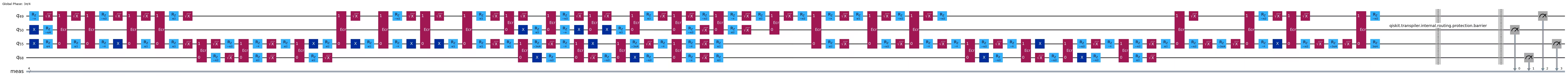

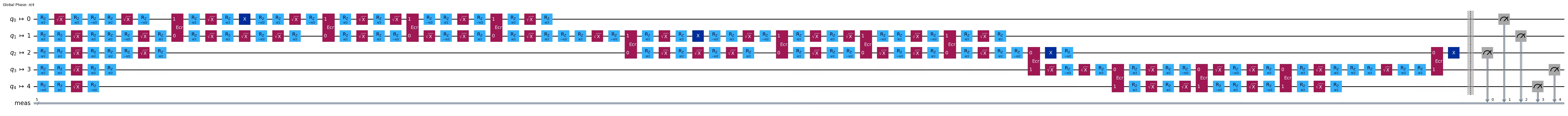

print("original synthesis:")

display(circ_org.draw("mpl", idle_wires=False, fold=-1))

print("new synthesis:")

display(circ_new.draw("mpl", idle_wires=False, fold=-1))

original synthesis:

new synthesis:

Ang bagong synthesis ay gumagawa ng mas mababaw na circuit. Bakit?

Ito ay dahil ang bagong circuit ay maaaring ilatag sa mga qubit na linearly connected, kaya pati na rin sa heavy-hexagon coupling graph ng IBM® Brisbane, habang ang orihinal na circuit ay nangangailangan ng star-shaped connectivity (isang degree-4 node) at kaya hindi maaaring ilatag sa heavy-hex coupling graph, na may mga node na may pinakamataas na degree 3. Bilang resulta, ang orihinal na circuit ay nangangailangan ng qubit routing na nagdadagdag ng mga SWAP gate, na nagpapalaki ng bilang ng mga gate.

Ang ginawa natin sa bagong circuit ay maaaring makita bilang isang manu-manong "coupling constraint-aware" na circuit synthesis. Sa ibang salita: manu-manong paglutas ng circuit synthesis at circuit mapping nang sabay-sabay.

# run the circuits

sampler = Sampler(backend=backend)

job = sampler.run([circ_org, circ_new], shots=10000)

print(f"Job ID: {job.job_id()}")

Job ID: 19d635b0-4d8b-44c2-a76e-49e4b9078b1b

# get results

result = job.result()

synthesis_org_result = result[0].data.meas.get_counts()

synthesis_new_result = result[1].data.meas.get_counts()

# plot

sim_result = {"0" * 5: 0.5, "1" * 5: 0.5}

plot_histogram(

[

result

for result in [

sim_result,

unoptimized_result,

synthesis_org_result,

synthesis_new_result,

]

],

bar_labels=False,

legend=[

"ideal",

"no optimization",

"synthesis_org",

"synthesis_new",

],

)

Sa pangkalahatan, ang circuit synthesis ay nakasalalay sa aplikasyon at napakahirap para sa isang software na masaklaw ang lahat ng posibleng aplikasyon. Ang Qiskit transpiler ay walang mga function para sa pag-synthesize ng GHZ state preparation circuit. Sa ganitong kaso, ang manu-manong circuit synthesis tulad ng ipinapakita sa itaas ay kapaki-pakinabang na isaalang-alang.

Sa seksyong ito, tiningnan natin ang mga detalye ng kung paano gumagana ang Qiskit transpiler gamit ang sumusunod na halimbawang toy circuit.

# Build a toy example circuit

from math import pi

import itertools

from qiskit.circuit import QuantumCircuit

from qiskit.circuit.library import excitation_preserving

circuit = QuantumCircuit(4, name="Example circuit")

circuit.append(excitation_preserving(4, reps=1, flatten=True), range(4))

circuit.measure_all()

value_cycle = itertools.cycle([0, pi / 4, pi / 2, 3 * pi / 4, pi, 2 * pi])

circuit.assign_parameters(

[x[1] for x in zip(range(len(circuit.parameters)), value_cycle)], inplace=True

)

circuit.draw("mpl")

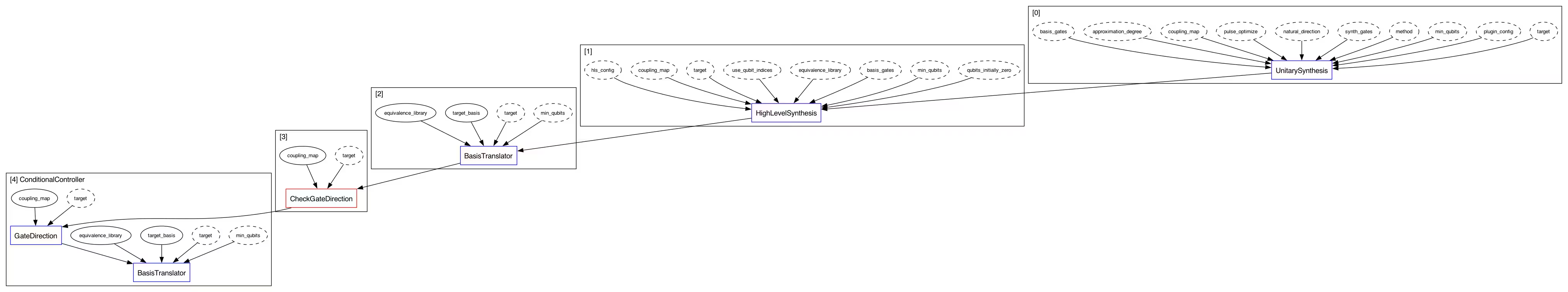

3.1 Iguhit ang buong Qiskit transpilation flow

Titingnan natin ang mga transpiler pass (gawain) para sa optimization_level=1.

from qiskit.transpiler.preset_passmanagers import generate_preset_pass_manager

# There is no need to read this entire image, but this outputs all the steps in the transpile() call

# for optimization level 1

pm = generate_preset_pass_manager(1, backend, seed_transpiler=42)

pm.draw()

Ang flow ay binubuo ng anim na yugto:

print(pm.stages)

('init', 'layout', 'routing', 'translation', 'optimization', 'scheduling')

3.2 Iguhit ang isang indibidwal na yugto

Una, iguhit natin ang lahat ng gawain (transpiler pass) na ginagawa sa init na yugto.

pm.init.draw()

Maaari nating patakbuhin ang bawat indibidwal na yugto. Patakbuhin natin ang init na yugto para sa ating circuit. Sa pamamagitan ng pagpapagana ng logger, makikita natin ang mga detalye ng pagpapatakbo.

import logging

logger = logging.getLogger()

logger.setLevel("INFO")

init_out = pm.init.run(circuit)

init_out.draw("mpl", fold=-1)

INFO:qiskit.passmanager.base_tasks:Pass: UnitarySynthesis - 0.03576 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: HighLevelSynthesis - 0.16618 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: BasisTranslator - 0.07176 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: InverseCancellation - 0.27299 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: ContractIdleWiresInControlFlow - 0.00811 (ms)

3.3 Ehersisyo

Iguhit ang mga pass ng layout na yugto at patakbuhin ang yugtong iyon para sa output circuit ng init na yugto (init_out), sa pamamagitan ng pagbabago ng mga cell na ginamit sa itaas.

Solusyon:

display(pm.layout.draw())

layout_out = pm.layout.run(init_out)

layout_out.draw("mpl", idle_wires=False, fold=-1)

INFO:qiskit.passmanager.base_tasks:Pass: SetLayout - 0.01001 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: TrivialLayout - 0.07129 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: CheckMap - 0.08917 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: VF2Layout - 1.24431 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: BarrierBeforeFinalMeasurements - 0.02599 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: SabreLayout - 5.11169 (ms)

Gawin din ang parehong bagay para sa translation na yugto.

Solusyon:

display(pm.translation.draw())

basis_out = pm.translation.run(layout_out)

basis_out.draw("mpl", idle_wires=False, fold=-1)

INFO:qiskit.passmanager.base_tasks:Pass: UnitarySynthesis - 0.03386 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: HighLevelSynthesis - 0.02718 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: BasisTranslator - 2.64192 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: CheckGateDirection - 0.02217 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: GateDirection - 0.36502 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: BasisTranslator - 0.64778 (ms)

Tandaan: Hindi palaging maaaring patakbuhin nang nagsasarili ang bawat indibidwal na yugto (dahil ang ilan sa kanila ay kailangang magdala ng impormasyon mula sa nakaraang yugto).

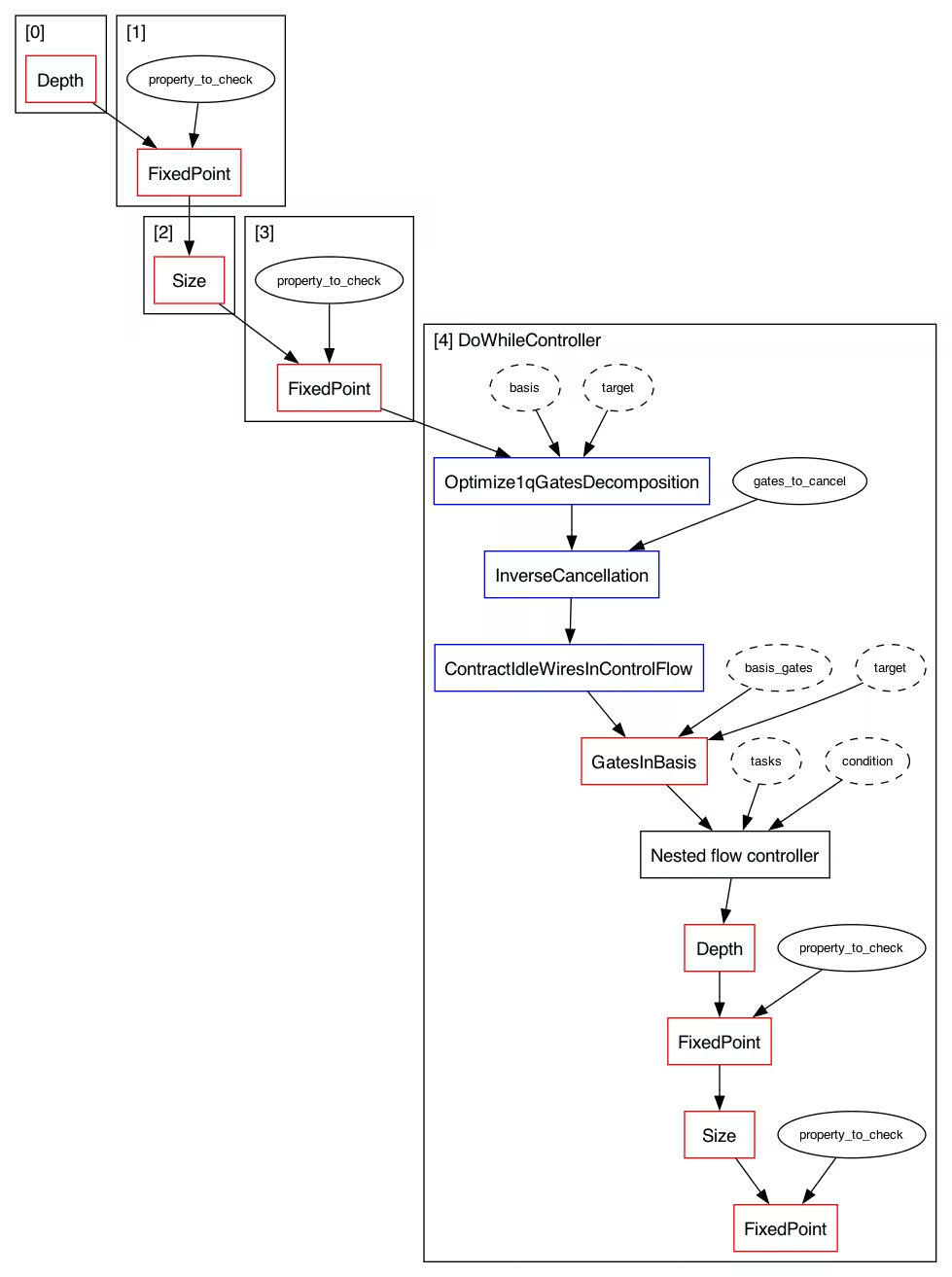

3.4 Optimization Stage

Ang huling default na yugto sa pipeline ay ang optimization. Pagkatapos nating i-embed ang circuit para sa target, lumawak na nang malaki ang circuit. Karamihan dito ay dahil sa mga hindi kahusayan sa mga equivalence relationship mula sa basis translation at swap insertion. Ginagamit ang optimization stage para subukang bawasan ang laki at lalim ng circuit. Nagpapatakbo ito ng serye ng mga pass sa isang do while loop hanggang maabot nito ang isang stable na output.

# pm.pre_optimization.draw()

pm.optimization.draw()

logger = logging.getLogger()

logger.setLevel("INFO")

opt_out = pm.optimization.run(basis_out)

INFO:qiskit.passmanager.base_tasks:Pass: Depth - 0.30112 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.03195 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Size - 0.01216 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.01001 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Optimize1qGatesDecomposition - 0.63729 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: InverseCancellation - 0.41723 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: ContractIdleWiresInControlFlow - 0.01192 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: GatesInBasis - 0.05484 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Depth - 0.08583 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.20599 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Size - 0.00787 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.00715 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Optimize1qGatesDecomposition - 0.16809 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: InverseCancellation - 0.17190 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: ContractIdleWiresInControlFlow - 0.00691 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: GatesInBasis - 0.02408 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Depth - 0.04935 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.00525 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Size - 0.00620 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.00286 (ms)

opt_out.draw("mpl", idle_wires=False, fold=-1)

4. Mga malalim na halimbawa

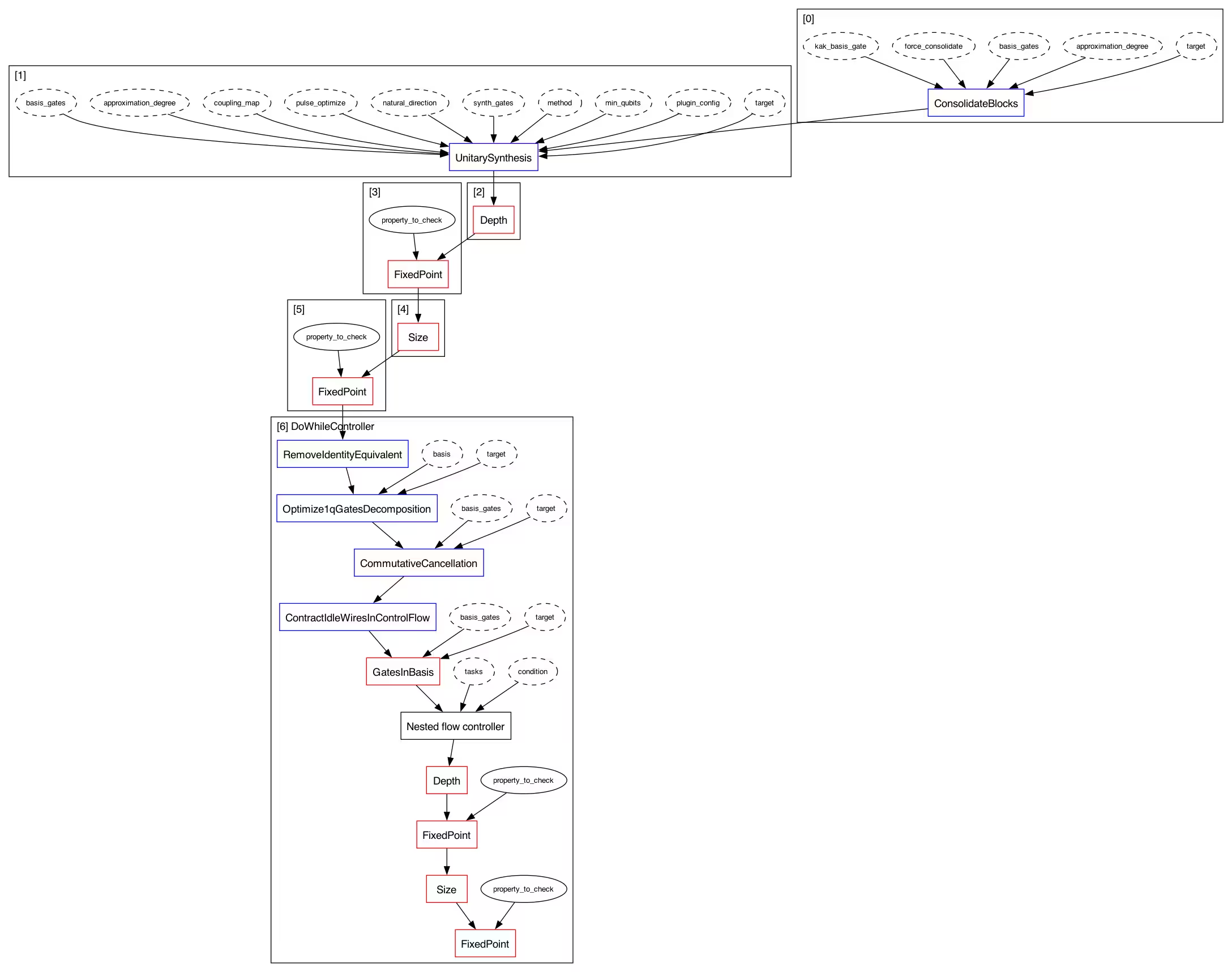

4.1 Dalawang-qubit block optimization gamit ang two-qubit unitary synthesis

Para sa level 2 at 3, mayroon kaming higit pang mga passes (Collect2qBlocks, ConsolidateBlocks, UnitarySynthesis) para sa mas maraming optimization, lalo na ang two-qubit block optimization. (Ikumpara ang optimization stage flow para sa level 2 sa nasa itaas para sa level 1)

Ang two-qubit block optimization ay binubuo ng dalawang hakbang: Ang pag-collect at pag-consolidate ng 2-qubit blocks, at ang pag-synthesize ng mga 2-qubit unitary matrices.

pm2 = generate_preset_pass_manager(2, backend, seed_transpiler=42)

pm2.optimization.draw()

from qiskit.transpiler import PassManager

from qiskit.transpiler.passes import (

Collect2qBlocks,

ConsolidateBlocks,

UnitarySynthesis,

)

# Collect 2q blocks and consolidate to unitary when we expect that we can reduce the 2q gate count for that unitary

consolidate_pm = PassManager(

[

Collect2qBlocks(),

ConsolidateBlocks(target=backend.target),

]

)

display(basis_out.draw("mpl", idle_wires=False, fold=-1))

consolidated = consolidate_pm.run(basis_out)

consolidated.draw("mpl", idle_wires=False, fold=-1)

# Synthesize unitaries

UnitarySynthesis(target=backend.target)(consolidated).draw(

"mpl", idle_wires=False, fold=-1

)

logger.setLevel("WARNING")

Nakita natin sa Part 2 na ang tunay na quantum compiler flow ay hindi ganoon kasimple at binubuo ito ng maraming passes (tasks). Ito ay pangunahing dahil sa software engineering na kailangan upang matiyak ang performance para sa malawak na hanay ng mga application circuits at ang maintainability ng software. Ang Qiskit transpiler ay karaniwang gumagana nang maayos sa karamihan ng mga kaso, ngunit kung makita mong hindi nao-optimize nang maigi ang iyong circuit ng Qiskit transpiler, magandang pagkakataon iyon para magsaliksik ng sarili mong application-specific circuit optimization gaya ng ipinakita sa Part 1. Ang teknolohiya ng Transpiler ay patuloy na umuunlad, at malugod na tinatanggap ang iyong kontribusyon sa R&D.

from qiskit.circuit import QuantumCircuit

from qiskit_ibm_runtime import QiskitRuntimeService, Sampler

service = QiskitRuntimeService()

backend = service.backend("ibm_brisbane")

sampler = Sampler(backend)

circ = QuantumCircuit(3)

circ.ccx(0, 1, 2)

circ.measure_all()

circ.draw("mpl")

sampler.run([circ]) # IBMInputValueError will be raised

4.2 Mahalaga ang Circuit optimization

Una, ikukumpara natin ang mga resulta ng pagpapatakbo ng mga 5-qubit GHZ state () preparation circuits na may at walang optimization.

from qiskit.circuit import QuantumCircuit

from qiskit.transpiler.preset_passmanagers import generate_preset_pass_manager

from qiskit_ibm_runtime import QiskitRuntimeService, Sampler

service = QiskitRuntimeService()

# backend = service.backend('ibm_brisbane')

backend = service.least_busy(

operational=True, simulator=False, min_num_qubits=127

) # Eagle

backend

Gagamit muna tayo ng GHZ Circuit na simpleng nai-synthesize tulad ng sumusunod.

num_qubits = 5

ghz_circ = QuantumCircuit(num_qubits)

ghz_circ.h(0)

[ghz_circ.cx(0, i) for i in range(1, num_qubits)]

ghz_circ.measure_all()

ghz_circ.draw("mpl")

Ita-transpile natin ang Circuit nang walang optimization (optimization_level=0) at may optimization (optimization_level=2).

Makikita mo, malaki ang pagkakaiba sa haba ng mga transpiled circuits.

pm0 = generate_preset_pass_manager(

optimization_level=0, backend=backend, seed_transpiler=777

)

pm2 = generate_preset_pass_manager(

optimization_level=2, backend=backend, seed_transpiler=777

)

circ0 = pm0.run(ghz_circ)

circ2 = pm2.run(ghz_circ)

print("optimization_level=0:")

display(circ0.draw("mpl", idle_wires=False, fold=-1))

print("optimization_level=2:")

display(circ2.draw("mpl", idle_wires=False, fold=-1))

optimization_level=0:

optimization_level=2:

# run the circuits

sampler = Sampler(backend)

job = sampler.run([circ0, circ2], shots=10000)

job_id = job.job_id()

print(f"Job ID: {job_id}")

Job ID: d13rnnemya70008ek1zg

# REPLACE WITH YOUR OWN JOB IDS

job = service.job(job_id)

# get results

result = job.result()

unoptimized_result = result[0].data.meas.get_counts()

optimized_result = result[1].data.meas.get_counts()

from qiskit.visualization import plot_histogram

# plot

sim_result = {"0" * 5: 0.5, "1" * 5: 0.5}

plot_histogram(

[result for result in [sim_result, unoptimized_result, optimized_result]],

bar_labels=False,

legend=[

"ideal",

"no optimization",

"with optimization",

],

)

4.3 Mahalaga ang Circuit synthesis

Susunod, ikukumpara natin ang mga resulta ng pagpapatakbo ng dalawang magkaibang nai-synthesize na 5-qubit GHZ state () preparation circuits.

# Original GHZ circuit (naive synthesis)

ghz_circ.draw("mpl")

# A better GHZ circuit (smarter synthesis), you learned in a previous lecture

ghz_circ2 = QuantumCircuit(5)

ghz_circ2.h(2)

ghz_circ2.cx(2, 1)

ghz_circ2.cx(2, 3)

ghz_circ2.cx(1, 0)

ghz_circ2.cx(3, 4)

ghz_circ2.measure_all()

ghz_circ2.draw("mpl")

circ_org = pm2.run(ghz_circ)

circ_new = pm2.run(ghz_circ2)

print("original synthesis:")

display(circ_org.draw("mpl", idle_wires=False, fold=-1))

print("new synthesis:")

display(circ_new.draw("mpl", idle_wires=False, fold=-1))

original synthesis:

new synthesis:

# run the circuits

sampler = Sampler(backend)

job = sampler.run([circ_org, circ_new], shots=10000)

job_id = job.job_id()

print(f"Job ID: {job_id}")

Job ID: d13rp283grvg008j12fg

# REPLACE WITH YOUR OWN JOB IDS

job = service.job(job_id)

# get results

result = job.result()

synthesis_org_result = result[0].data.meas.get_counts()

synthesis_new_result = result[1].data.meas.get_counts()

# plot

sim_result = {"0" * 5: 0.5, "1" * 5: 0.5}

plot_histogram(

[result for result in [sim_result, synthesis_org_result, synthesis_new_result]],

bar_labels=False,

legend=[

"ideal",

"synthesis_org",

"synthesis_new",

],

)

4.4 Pangkalahatang 1-qubit gate decomposition

from qiskit import QuantumCircuit, transpile

from qiskit.circuit import Parameter

from qiskit.circuit.library.standard_gates import UGate

phi, theta, lam = Parameter("φ"), Parameter("θ"), Parameter("λ")

qc = QuantumCircuit(1)

qc.append(UGate(theta, phi, lam), [0])

qc.draw(output="mpl")

transpile(qc, basis_gates=["rz", "sx"]).draw(output="mpl")

4.5 One-qubit block optimization

from qiskit import QuantumCircuit

qc = QuantumCircuit(1)

qc.x(0)

qc.y(0)

qc.z(0)

qc.rx(1.23, 0)

qc.ry(1.23, 0)

qc.rz(1.23, 0)

qc.h(0)

qc.s(0)

qc.t(0)

qc.sx(0)

qc.sdg(0)

qc.tdg(0)

qc.draw(output="mpl")

from qiskit.quantum_info import Operator

Operator(qc)

Operator([[ 0.45292511-0.57266982j, -0.66852684-0.14135058j],

[ 0.14135058+0.66852684j, -0.57266982+0.45292511j]],

input_dims=(2,), output_dims=(2,))

from qiskit import transpile

qc_opt = transpile(qc, basis_gates=["rz", "sx"])

qc_opt.draw(output="mpl")

Operator(qc_opt)

Operator([[ 0.45292511-0.57266982j, -0.66852684-0.14135058j],

[ 0.14135058+0.66852684j, -0.57266982+0.45292511j]],

input_dims=(2,), output_dims=(2,))

Operator(qc).equiv(Operator(qc_opt))

True

4.6 Toffoli decomposition

qc = QuantumCircuit(3)

qc.ccx(0, 1, 2)

qc.draw(output="mpl")

from qiskit import QuantumCircuit, transpile

qc = QuantumCircuit(3)

qc.ccx(0, 1, 2)

qc = transpile(qc, basis_gates=["rz", "sx", "cx"])

qc.draw(output="mpl")

4.7 CU gate decomposition

from qiskit.circuit.library.standard_gates import CUGate

phi, theta, lam, gamma = Parameter("φ"), Parameter("θ"), Parameter("λ"), Parameter("γ")

qc = QuantumCircuit(2)

# qc.cu(theta, phi, lam, gamma, 0, 1)

qc.append(CUGate(theta, phi, lam, gamma), [0, 1])

qc.draw(output="mpl")

from qiskit.circuit.library.standard_gates import CUGate

phi, theta, lam, gamma = Parameter("φ"), Parameter("θ"), Parameter("λ"), Parameter("γ")

qc = QuantumCircuit(2)

qc.append(CUGate(theta, phi, lam, gamma), [0, 1])

qc = transpile(qc, basis_gates=["rz", "sx", "cx"])

qc.draw(output="mpl")

4.8 CX, ECR, CZ ay pantay-pantay hanggang sa local Cliffords

Tandaan na ang (Hadamard), ( Z-rotation), ( Z-rotation), (Pauli X) ay mga Clifford gates.

qc = QuantumCircuit(2)

qc.cx(0, 1)

qc.draw(output="mpl", style="bw")

qc = QuantumCircuit(2)

qc.cx(0, 1)

transpile(qc, basis_gates=["x", "s", "h", "sdg", "ecr"]).draw(output="mpl", style="bw")

qc = QuantumCircuit(2)

qc.cx(0, 1)

transpile(qc, basis_gates=["h", "cz"]).draw(output="mpl", style="bw")

Gamit ang IBM backend 1q basis gates na "rz", "sx" at "x".

qc = QuantumCircuit(2)

qc.cx(0, 1)

transpile(qc, basis_gates=["rz", "sx", "x", "ecr"]).draw(output="mpl", style="bw")

qc = QuantumCircuit(2)

qc.cx(0, 1)

transpile(qc, basis_gates=["rz", "sx", "x", "cz"]).draw(output="mpl", style="bw")

# Check Qiskit version

import qiskit

qiskit.__version__

'2.0.2'